Low Skew 1:6 Clock Driver

### **Product Features:**

- Six low skew outputs: 0.35 ns (typ.)

- XTAL oscillator interface: 35 MHz (max.)

- Clock input interface: 66 MHz (max.)

- 3.3V supply voltage

- High speed: 3.5 ns propagation delay

- 5.0V tolerant enable inputs

- Packages available:

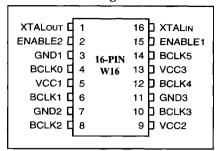

- 16-pin 150-mil wide SOIC (W16)

## **Product Description:**

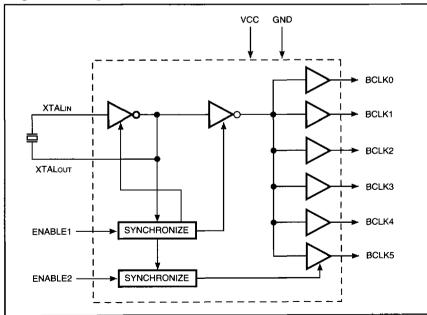

The PI6B3904 is a low skew 1:6 clock driver. It is designed to provide the requisite clocks for a PCI buses in either a 5V or 3.3V PCI signaling environment.

The PI6B3904 operates from a 3.3V supply and can interface to either a TTL clock input or an external crystal. The inputs can be driven with 5.0V when the Vcc is at 3.3V. The outputs meet all of the PCI standards specifications.

The PI6B3904 offers two synchronous enable inputs. Both enable signals are active HIGH. A logic "0" on the ENABLE1 input will disable the BCLK[4-0] outputs. A logic "0" on the ENABLE2 input will disable the BCLK5 output.

The enable signals can be used to disable the device for system power savings during periods of inactivity. Output disabling will happen only when the BCLK[4-0] outputs are already LOW. This feature guarantees that there will be no runt pulses during the enable and disable process.

# Logic Block Diagram

543 PS7011A 12/15/95

# **Product Pin Configuration**

## **Product Pin Description**

| Pin Name           | Description                                   |

|--------------------|-----------------------------------------------|

| XTALin             | XTAL Input                                    |

| XTALout            | XTAL Output. 180° phase shift from XTAL pins. |

| ENABLE1<br>ENABLE2 | Enable pins control BLCK5-<br>BLCK0 outputs   |

| BLCK5-0            | Clock outputs. Same as input frequency        |

| Vcc                | Power supply                                  |

| GND                | Ground                                        |

# **Function Description**

| ENABLE1(1) | ENABLE2(1) | BLCK4-0<br>Output | BLCK5<br>Output | OSC (on/off) |

|------------|------------|-------------------|-----------------|--------------|

| 0          | 0          | LOW               | LOW             | Off          |

| 0          | 1          | LOW               | XTALIN          | On           |

| 1          | 0          | XTALIN            | LOW             | On           |

| 1          | 1          | XTALIN            | XTALIN          | On           |

#### Notes

## **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature                    | 65°C to +150°C    |

|----------------------------------------|-------------------|

| Ambient Temperature with Power Applied | 0°C to +70°C      |

| Input Voltage                          | 0.5V to Vcc +0.5V |

| Supply Voltage                         | 0.5V to +4.6V     |

| DC Output Current                      | 120 mA            |

| Power Dissipation (ENABLE1/2 = 1)      | TBD mW            |

| Power Dissipation (ENABLE1/2 = 0)      | 40 μW             |

### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1.</sup> ENABLE1, ENABLE2 skew during logic switching from 10 to 01 should not cause the OSC to shut off.

# **DC Electrical Characteristics** (Over the Operating Range, $TA = 0^{\circ}C$ to $+70^{\circ}C$ , $VCC = 3.3V \pm 0.3V$ )

| Parameters | Description         | Test Conditions(1)                         |                                | Min. | Тур | Max. | Units |

|------------|---------------------|--------------------------------------------|--------------------------------|------|-----|------|-------|

| Vон        | Output HIGH Voltage | Vcc = Min., Vin = ViH or ViL               | $IoH = -36.0 \text{ mA}^{(2)}$ | 2.4  | _   | _    | v     |

| Vol        | Output LOW Current  | Vcc = Min., Vin = Vih or Vil               | IoL = 36 mA                    |      |     | 0.4  | v     |

| ViH        | Input HIGH Voltage  | Guaranteed Logic HIGH Level <sup>(3)</sup> |                                | 2.0  |     | 5.5  | v     |

| Vil        | Input LOW Voltage   | Guaranteed Logic LOW Level                 |                                |      | -   | 0.8  | v     |

| Іін        | Input HIGH Current  | Vcc = Max.                                 |                                |      |     | 2.5  | μА    |

| IIL        | Input LOW Current   | Vcc = Max.                                 |                                | _    |     | 2.5  | μΑ    |

## Capacitance ( $T_A = 25^{\circ}C$ , f = 1 MHz)

| Parameters | Description       | <b>Test Conditions</b> | Тур | Max. | Units |

|------------|-------------------|------------------------|-----|------|-------|

| Cin        | Input Capacitance | XTALin                 | _   | 9.0  | pF    |

|            |                   | Others                 |     | 4.5  | pF    |

#### Notes:

- 1. For conditions show as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. The outputs can drive series terminated or parallel  $50\Omega$  (or  $50\Omega$  to Vcc/2) transmission lines on the incident edge.

- 3. XTALIN input will sink up to 10 mA when driven to 5.5V. There are no reliability concerns associated with the condition. Note that the Enable1 input must be a logic HIGH. Do not take the Enable1 input to a logic LOW with >Vcc volts on the XTALIN input.

## **Recommended Operating Conditions**

| Parameters | Description                                                   | Min.  | Max.  | Units                  |

|------------|---------------------------------------------------------------|-------|-------|------------------------|

| TA         | Ambient Temperature                                           | 0     | 70    | °C                     |

| Vec        | Positive Supply Voltage (Functional Range)                    | 3.0   | 3.6   | v                      |

| SYNC       | Input Frequency in XTALin (SYNC Vih = 2.0V, Vil = 0.8V        | DC    | 66    | MHz                    |

| tr, tr     | Input Rise or Fall Time                                       | 3     | _     | ns                     |

| SYNC       | tнібн (@ SYNC Input) when using external source for reference | 0.44T | 0.56T | (T is the time period) |

| SYNC       | tLow (@ SYNC Input) when using external source for reference  | 0.44T | 0.56T | (T is the time period) |

## **Power Supply Characteristics**

| Parameters  | Description                    | Test Conditions(1) | Min. | Тур. | Max. | Units |

|-------------|--------------------------------|--------------------|------|------|------|-------|

| <b>I</b> cc | Quiescent Power <sup>(2)</sup> | DC                 | _    | 20   |      | μΑ    |

|             | Supply Current(3)              | 33 MHz             | _    | 50   | 60   | mA    |

#### Notes:

- 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device.

- 2. P16B3904 with no loading using a 33 MHz crystal. Enable 1 = Enable 2 = 0. Power supply current increases with output frequency and output load conditions.

- 3. P16B3904 with no loading using a 33 MHz crystal. Enable1 = Enable2 = 1. Power supply current increases with output frequency and output load conditions.

## **Dynamic Operating Conditions** (TA = $0^{\circ}$ C to $+70^{\circ}$ C, Vcc = 3.3V $\pm 0.3$ V)

| Parameters    | Description                                                                                                          | Min.            | Max.              | Units                   |

|---------------|----------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-------------------------|

| f             | Frequency Range                                                                                                      | DC              | 66                | MHz                     |

| tH            | High Time (Time above 2.0V at the load end of transmission line)                                                     | 0.4T            | 0.6T              | T is the time period    |

| tL            | Low Time (Time below 0.8V at the load end of transmission line)                                                      | 0.4T            | 0.6T              | T is the time period    |

| Period (min.) | Time from 1.5V to next 1.5V at the end of transmission line                                                          | T – 400 ps      |                   | T is the average period |

| SKR           | Skew Rise Time                                                                                                       | _               | 400               | ps                      |

| SKF           | Skew Fall Time                                                                                                       |                 | 500               | ps                      |

| tr            | Rise Time: 0.4V to 2.4V (Unloaded Output)                                                                            | 1               | 4                 | V/ns                    |

| tr            | Fall Time: 2.4V to 0.4V (Unloaded Output)                                                                            | 1               | 4                 | V/ns                    |

| ton           | Start-up Time. Time to start the oscillator on and Enable only CLK Output.                                           | _               | 5                 | ms                      |

| toff          | Disable Time. Time to disable any CLK output and shut off the oscillator.                                            |                 | 4                 | Cycles                  |

| ten           | Enable CLKon Time. Time to enable any CLK output. (Oscillator is already ON)                                         |                 | 4                 | Cycles                  |

| tDIS          | Disable CLKoff Time. Time to disable any CLK output. (Oscillator stays ON)                                           |                 | 4                 | Cycles                  |

| CLOAD         | 1 or 2 Series Terminated Lines Transmission Line Zout Termination Matched Series Resistor Capacitance at Load Device | 60<br>Zouт<br>5 | 100<br>Zout<br>12 | Ω<br>Ω<br>pF            |

| DRT           | Round Trip Delay Clock Lines. The lesser of or                                                                       | _               | 12<br>T/2 – 1     | ns<br>ns                |

| Ogain         | Oscillator Cell Gain. XTALIN to XTALOUT (Must oscillate with a XTAL of 70Ω (max) Series Resistance                   | 6               |                   | dB                      |

| SLP           | Loop Phase Shift. Modulo 360° + (Oscillator Cell: Inverter and XTAL Network)                                         | 30              |                   | °C                      |

| RF            | XTAL Feedback Resistor, XTALIN to XTALOUT                                                                            | 200K            | 1M                | Ω                       |

| Rs            | XTAL Source Impedance of XTALout                                                                                     | 75              | 125               | Ω                       |

| Ds            | Driver Source Impedance of Clock Outputs                                                                             | 4               | 10                | Ω                       |

### Notes:

- 1. Each Skew spec forms a window of specified time in which all output transitions must occur. Skew measurements should assume loading as described in notes 2 and 3.

- 2. Cycle to Cycle Jitter. The jitter is not defined separately from the High/Low time or the Period. The duty cycle and the Jitter must be such that the HIGH Time, LOW Time, and Minimum Period are met. In determining the effect of the jitter, it is requested that the 'peak' value be that level which occurs once in 10Exp15 events. If the Jitter were Gaussian, this would correspond to 8 sigma.

- 3. Alignment Jitter: Any dynamic Jitter terms that effect output to output skew shall be accounted for in the Skew spec. As with cycle to cycle Jitter, the level of Jitter that should be accounted for is one occurrence in 10EXP15 events.

PS7011A 12/15/95